Data Sheet

FlashFlex51 MCU

SST89E52RD2/RD / SST89E54RD2/RD / SST89E58RD2/RD

SST89V52RD2/RD / SST89V54RD2/RD / SST89V58RD2/RD

65

©2006 Silicon Storage Technology, Inc. S71255-05-000 5/06

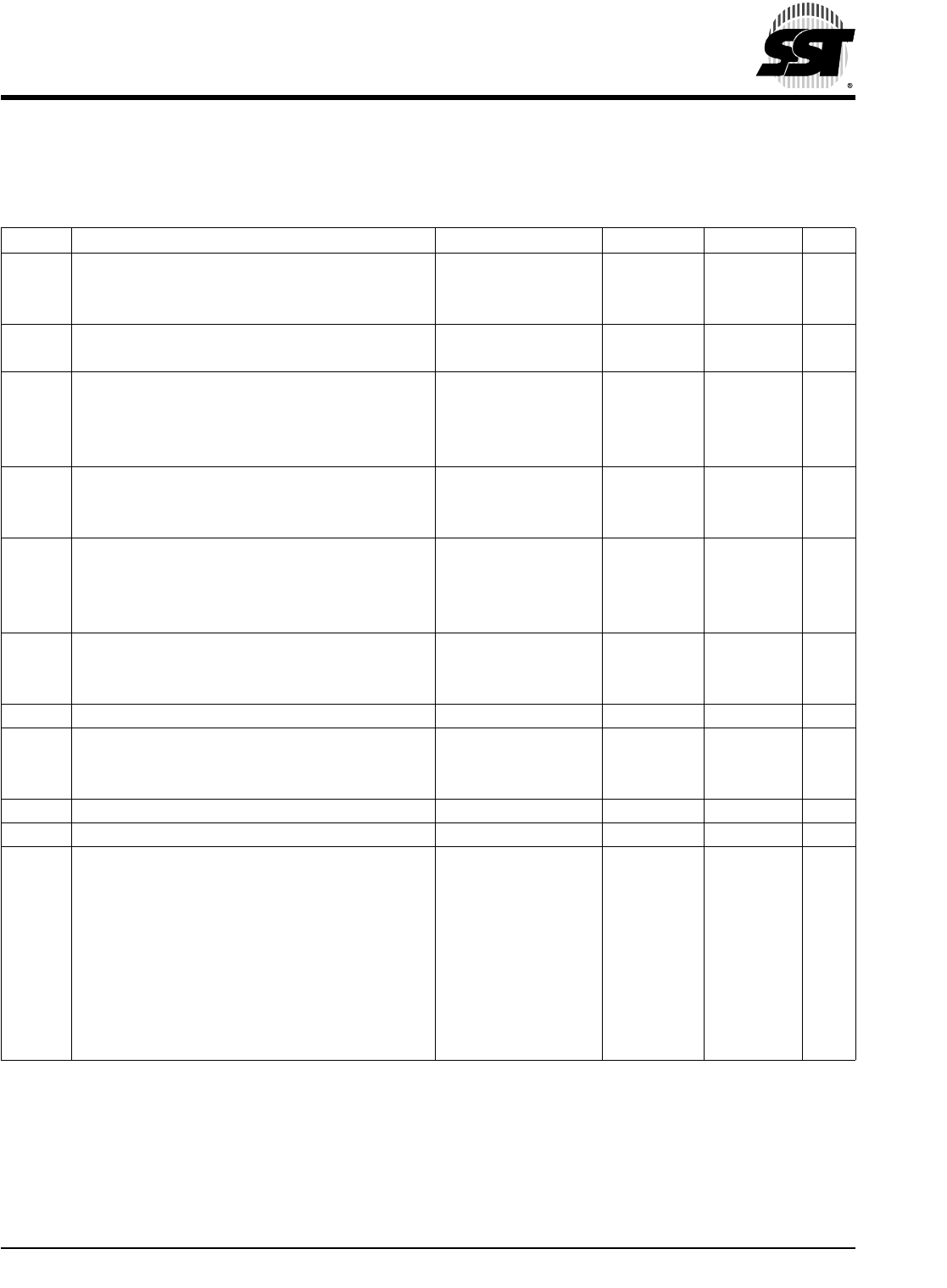

14.1 DC Electrical Characteristics

TABLE 14-6: DC Electrical Characteristics for SST89E5xRD2/RD

T

A

= -40°C to +85°C; V

DD

= 4.5-5.5V; V

SS

= 0V

Symbol Parameter Test Conditions Min Max Units

V

IL

Input Low Voltage 4.5 < V

DD

< 5.5 -0.5 0.2V

DD

- 0.1 V

V

IH

Input High Voltage 4.5 < V

DD

< 5.5 0.2V

DD

+ 0.9 V

DD

+ 0.5 V

V

IH1

Input High Voltage (XTAL1, RST) 4.5 < V

DD

< 5.5 0.7V

DD

V

DD

+ 0.5 V

V

OL

Output Low Voltage (Ports 1.5, 1.6, 1.7) V

DD

= 4.5V

I

OL

= 16mA 1.0 V

V

OL

Output Low Voltage (Ports 1, 2, 3)

1

1. Under steady state (non-transient) conditions, I

OL

must be externally limited as follows:

Maximum I

OL

per port pin: 15mA

Maximum I

OL

per 8-bit port:26mA

Maximum I

OL

total for all outputs:71mA

If I

OL

exceeds the test condition, V

OL

may exceed the related specification.

Pins are not guaranteed to sink current greater than the listed test conditions.

V

DD

= 4.5V

I

OL

= 100µA

2

0.3 V

I

OL

= 1.6mA

2

0.45 V

I

OL

= 3.5mA

2

1.0 V

V

OL1

Output Low Voltage (Port 0, ALE, PSEN#)

1,3

V

DD

= 4.5V

I

OL

= 200µA

2

0.3 V

I

OL

= 3.2mA

2

0.45 V

V

OH

Output High Voltage (Ports 1, 2, 3, ALE, PSEN#)

4

V

DD

= 4.5V

I

OH

= -10µA V

DD

- 0.3 V

I

OH

= -30µA V

DD

- 0.7 V

I

OH

= -60µA V

DD

- 1.5 V

V

OH1

Output High Voltage (Port 0 in External Bus Mode)

4

V

DD

= 4.5V

I

OH

= -200µA V

DD

- 0.3 V

I

OH

= -3.2mA V

DD

- 0.7 V

V

BOD

Brown-out Detection Voltage 3.85 4.15 V

I

IL

Logical 0 Input Current (Ports 1, 2, 3) V

IN

= 0.4V -75 µA

I

TL

Logical 1-to-0 Transition Current (Ports 1, 2, 3)

5

V

IN

= 2V -650 µA

I

LI

Input Leakage Current (Port 0) 0.45 < V

IN

< V

DD

-0.3 ±10 µA

R

RST

RST Pull-down Resistor 40 225 KΩ

C

IO

Pin Capacitance

6

@ 1 MHz, 25°C 15 pF

I

DD

Power Supply Current

IAP Mode

@ 40 MHz 88 mA

Active Mode

@ 40 MHz 50 mA

Idle Mode

@ 40 MHz 42 mA

Power-down Mode T

A

= 0°C to +70°C 80 µA

T

A

= -40°C to +85°C 90 µA

T14-6.2 1255