©2006 Fairchild Semiconductor Corporation

1

www.fairchildsemi.com

February 2006

74LCX373 Rev. 2.0.0

74LCX373 Low Voltage Octal Transparent Latch with 5V Tolerant Inputs and Outputs

74LCX373

Low Voltage Octal Transparent Latch

with 5V Tolerant Inputs and Outputs

Features

■

5V tolerant inputs and outputs

■

2.3V–3.6V V

CC

specifications provided

■

8.0ns t

PD

max (V

CC

= 3.3V), 10

µ

A I

CC

max

■

Power down high impedance inputs and outputs

■

Supports live insertion/withdrawal

1

■

±

24mA output drive (V

CC

= 3.0V)

■

Implements patented noise/EMI reduction circuitry

■

Latch-up performance exceeds JEDEC 78 conditions

■

ESD performance

– Human body model

>

2000V

– Machine model

>

200V

■

Leadless Pb-Free DQFN package

General Description

The LCX373 consists of eight latches with 3-STATE out-

puts for bus organized system applications. The device is

designed for low voltage applications with capability of

interfacing to a 5V signal environment.

The LCX373 is fabricated with an advanced CMOS tech-

nology to achieve high speed operation while maintain-

ing CMOS low power dissipation.

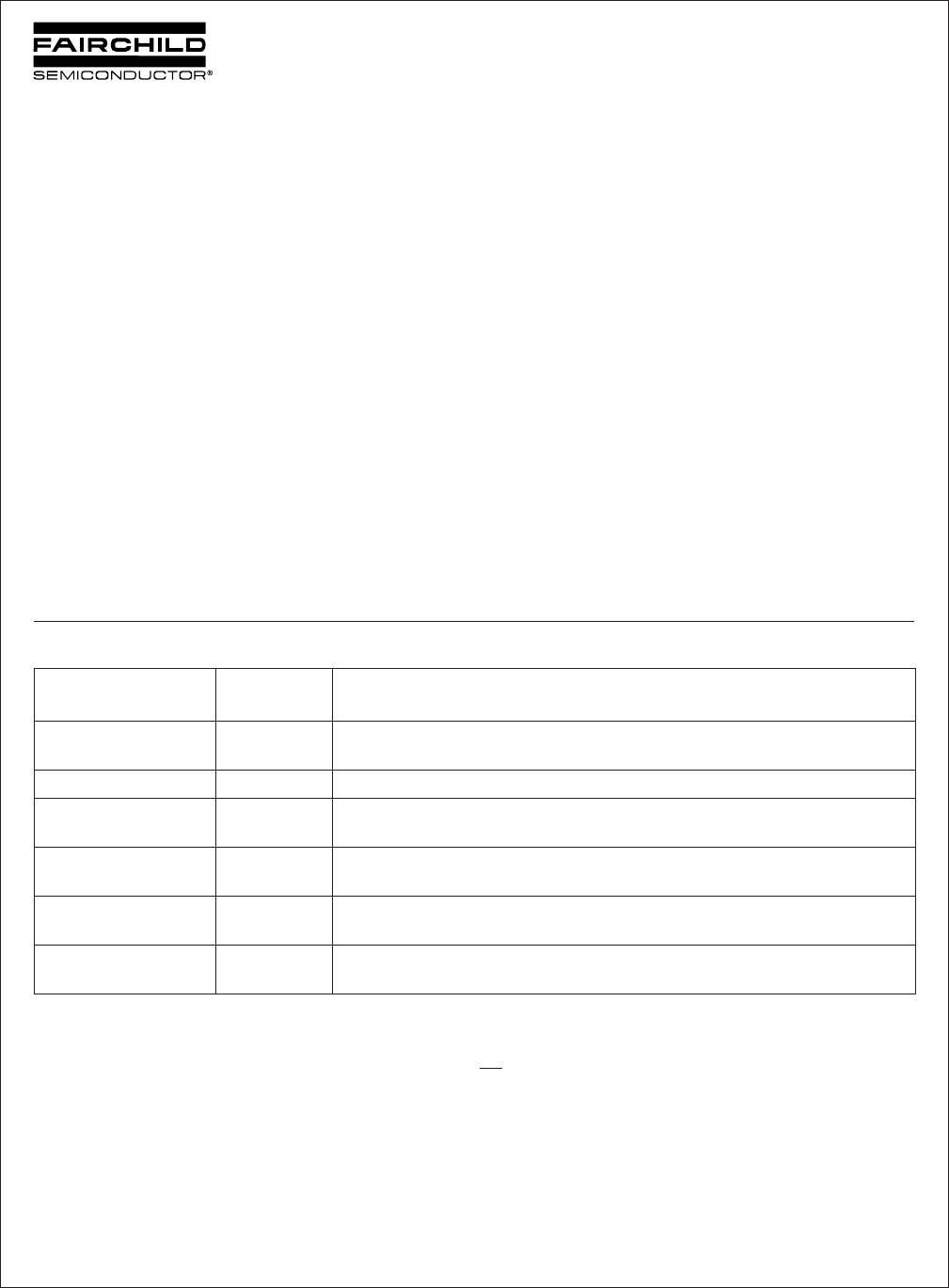

Ordering Information

Devices also available in Tape and Reel. Specify by appending the suffix letter “X” to the ordering code.

Pb-Free package per JEDEC J-STD-020B.

Notes:

1. To ensure the high impedance state during power up or down, OE

should be tied to V

CC

through a pull-up resistor: the minimum

value of the resistor is determined by the current-sourcing capability of the driver.

2. DQFN package available in Tape and Reel only.

3. “_NL” indicates Pb-Free package (per JEDEC J-STD-020B). Device available in Tape and Reel only.

Order

Number

Package

Number Package Description

74LCX373WM M20B 20-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-013, 0.300"

Wide

74LCX373SJ M20D Pb-Free 20-Lead Small Outline Package (SOP), EIAJ TYPE II, 5.3mm Wide

74LCX373BQX

2

MLP020B Pb-Free 20-Terminal Depopulated Quad Very-Thin Flat Pack No Leads

(DQFN), JEDEC MO-241, 2.5 x 4.5mm

74LCX373MSA MSA20 20-Lead Shrink Small Outline Package (SSOP), JEDEC MO-150, 5.3mm

Wide

74LCX373MTC MTC20 20-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153,

4.4mm Wide

74LCX373MTCX_NL

3

MTC20 Pb-Free 20-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC

MO-153, 4.4mm Wide