www.fairchildsemi.com 2

74F675A

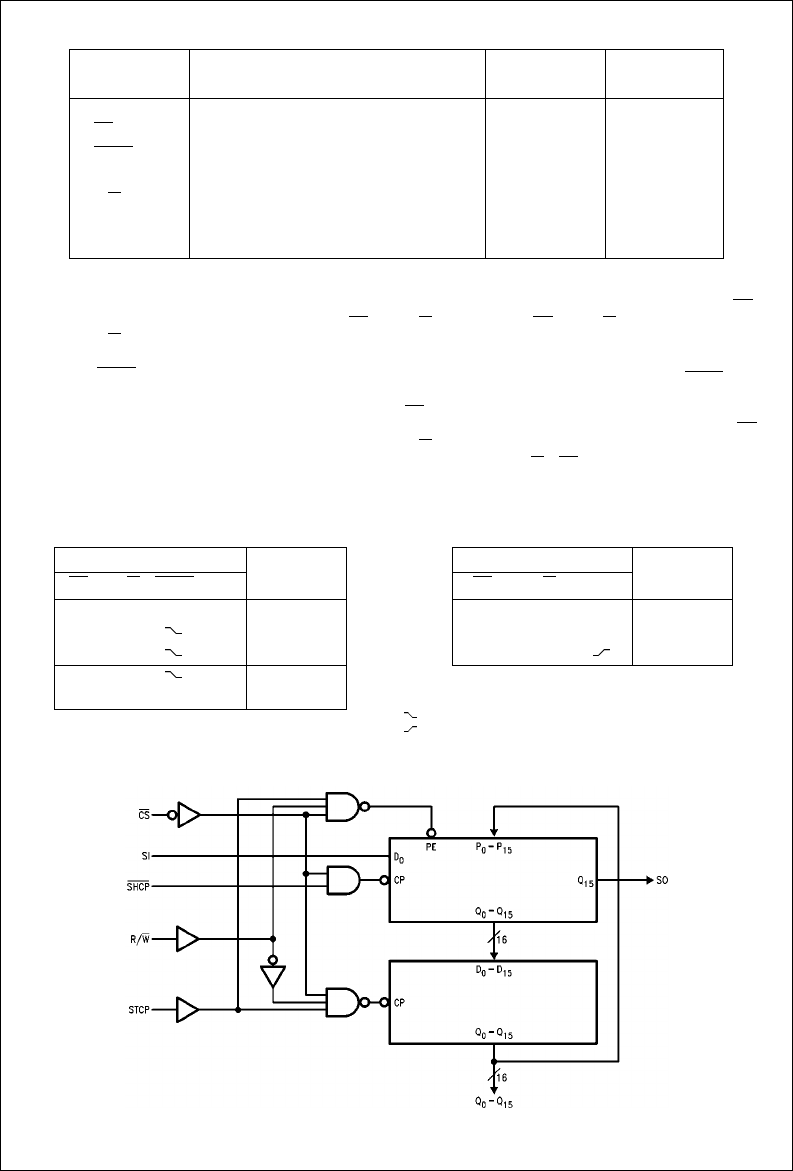

Unit Loading/Fan Out

Functional Description

The 16-Bit shift register operates in one of four modes, as

determined by the signals applied to the Chip Select (CS

),

Read/Write (R/W

) and Store Clock Pulse (STCP) input.

State changes are indicated by the falling edge of the Shift

Clock Pulse (SHCP

). In the Shift Right mode, data enters

D

0

from the Serial Input (SI) pin and exits from Q

15

via the

Serial Data Output (SO) pin. In the Parallel Load mode,

data from the storage register outputs enter the shift regis-

ter and serial shifting is inhibited.

The storage register is in the Hold mode when either CS

or

R/W

is HIGH. With CS and R/W both LOW, the storage

register is parallel loaded from the shift register on the ris-

ing edge of STCP.

To prevent false clocking of the shift register, SHCP

should

be in the LOW state during a LOW-to-HIGH transition of

CS

. To prevent false clocking of the storage register, STCP

should be LOW during a HIGH-to-LOW transition of CS

if

R/W

is LOW, and should also be LOW during a HIGH-to-

LOW transition of R/W

if CS is LOW.

Shift Register Operations Table Storage Register Operations Table

H = HIGH Voltage Level

L = LOW Voltage Level

X = Immaterial

= HIGH-to-LOW Transition

= LOW-to-HIGH Transition

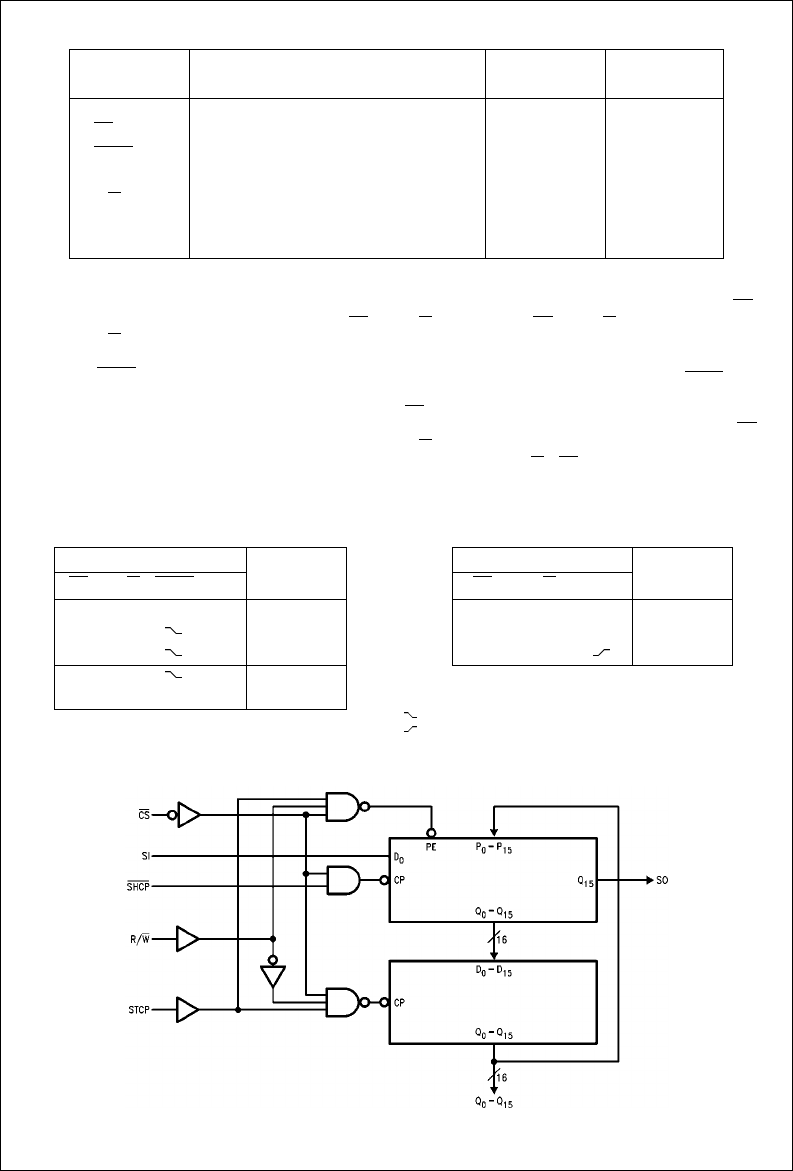

Logic Diagram

Please note that this diagram is provided only for the understanding of logic operations and should not be used to estimate propagation delays.

Pin Names Description

U.L.

Input I

IH

/I

IL

HIGH/LOW

Output I

OH

/I

OL

SI Serial Data Input 1.0/1.0 20 µA/−0.6 mA

CS

Chip Select Input (Active LOW) 1.0/1.0 20 µA/−0.6 mA

SHCP

Shift Clock Pulse Input (Active Falling Edge) 1.0/1.0 20 µA/−0.6 mA

STCP Store Clock Pulse Input (Active Rising Edge) 1.0/1.0 20 µA/−0.6 mA

R/W

Read/Write Input 1.0/1.0 20 µA/−0.6 mA

SO Serial Data Output 50/33.3 −1 mA/20 mA

Q

0

–Q

15

Parallel Data Outputs 50/33.3 −1 mA/20 mA

Control Inputs Operating

CS

R/W SHCP STCP Mode

H X X X Hold

LL

X Shift Right

LH

L Shift Right

LH

H Parallel Load,

No Shifting

Inputs Operating

CS

R/W STCP Mode

HXXHold

LHXHold

LL

Parallel Load