© 2004 Fairchild Semiconductor Corporation DS009551 www.fairchildsemi.com

April 1988

Revised January 2004

74F538 1-of-8 Decoder with 3-STATE Outputs

74F538

1-of-8 Decoder with 3-STATE Outputs

General Description

The 74F538 decoder/demultiplexer accepts three Address

(A

0

–A

2

) input signals and decodes them to select one of

eight mutually exclusive outputs. A polarity control input (P)

determines whether the outputs are active LOW or active

HIGH. A HIGH Signal on either of the active LOW Output

Enable (OE

) inputs forces all outputs to the high imped-

ance state. Two active HIGH and two active LOW input

enables are available for easy expansion to 1-of 32 decod-

ing with four packages, or for data demultiplexing to 1-of-8

or 1-of-16 destinations.

Features

■ Output polarity control

■ Data demultiplexing capability

■ Multiple enables for expansion

■ 3-STATE outputs

Ordering Code:

Devices also available in Tape and Reel. Specify by appending the suffix letter “X” to the ordering code.

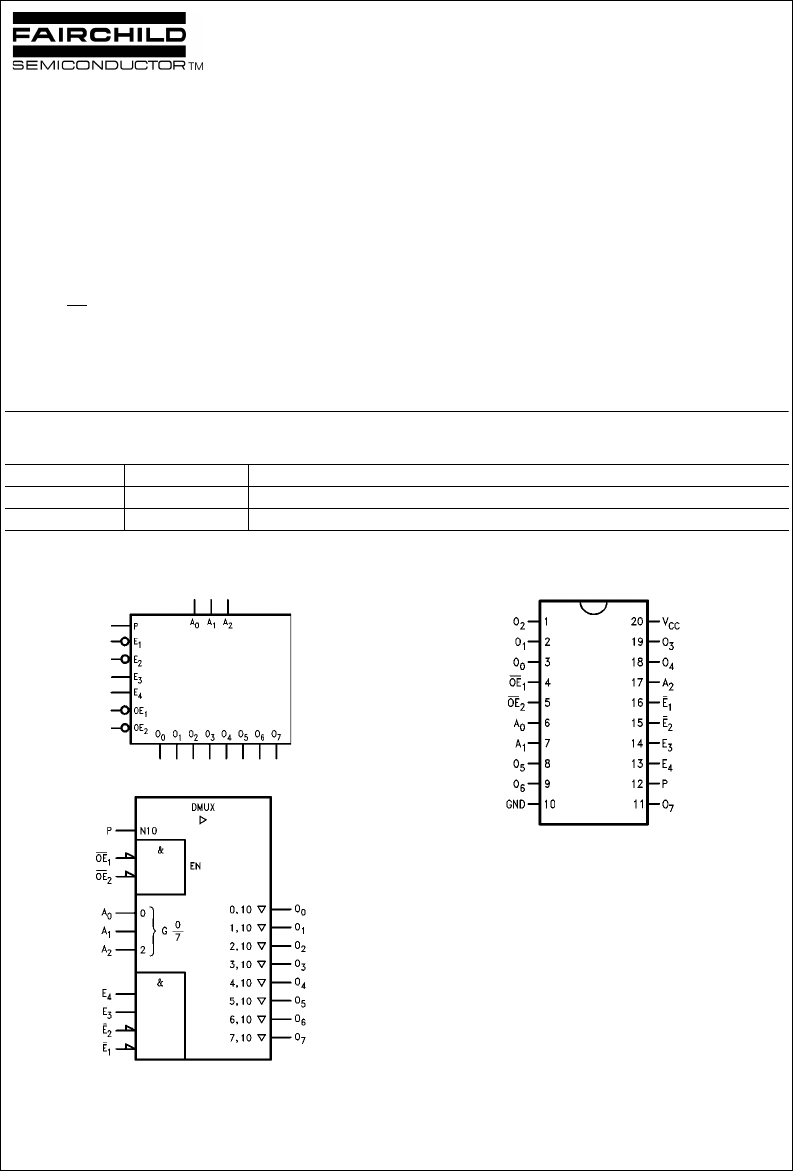

Logic Symbols

IEEE/IEC

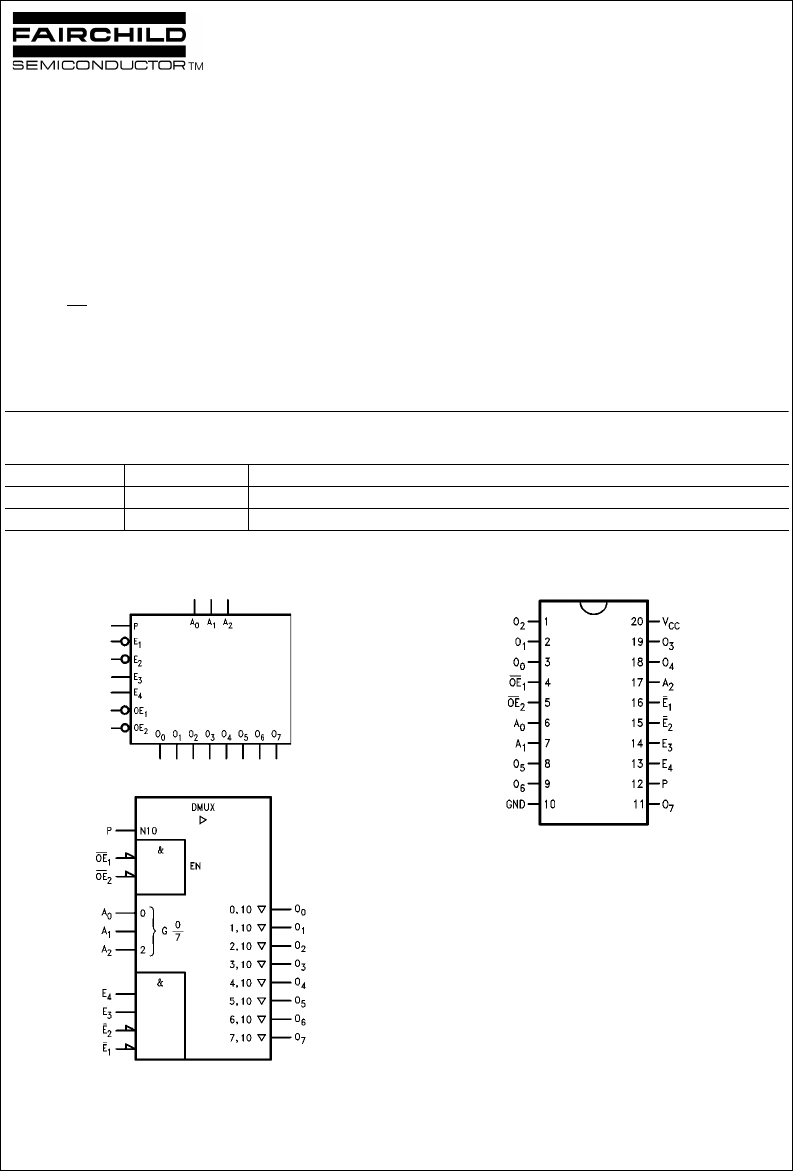

Connection Diagram

Order Number Package Number Package Description

74F538SC M20B 20-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-013, 0.300" Wide

74F538PC N20A 20-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300" Wide