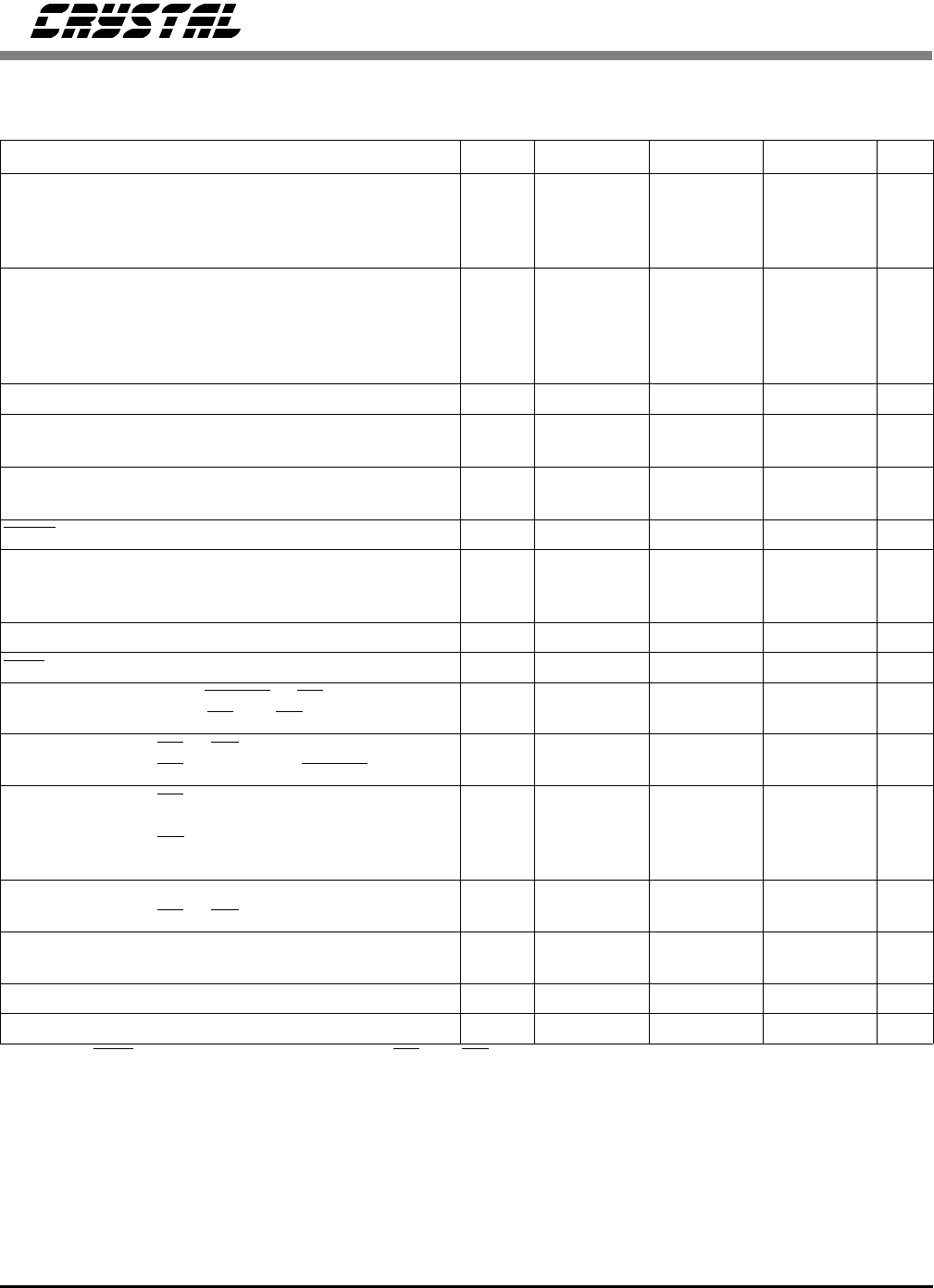

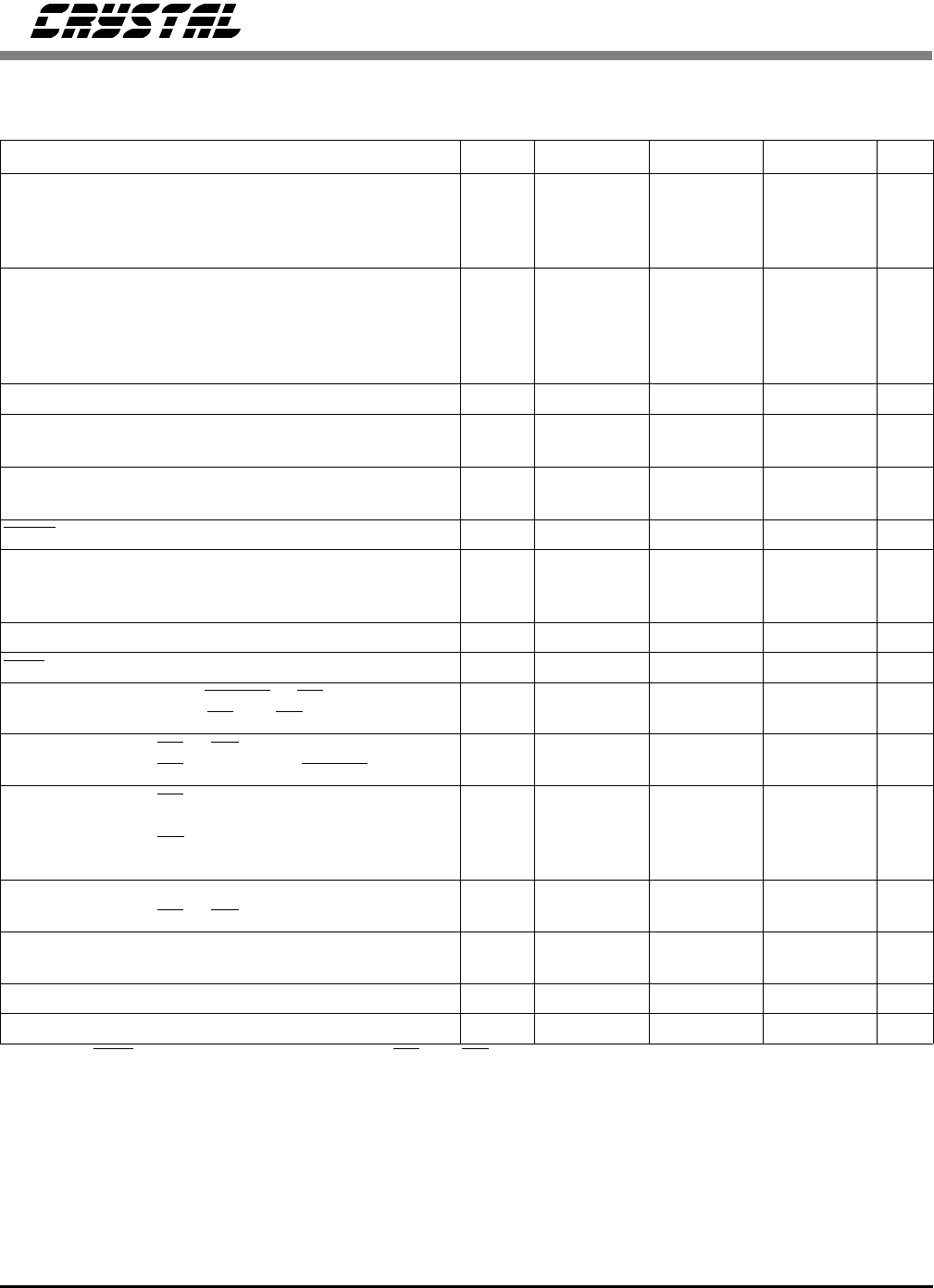

SWITCHING CHARACTERISTICS

(T

A

= T

MIN

to T

MAX

; VA+, VD+ = 5V ±10%;

VA-, VD- = -5V ±10%; Inputs: Logic 0 = 0V, Logic 1 = VD+; C

L

= 50 pF, BW = VD+)

Parameter Symbol Min Typ Max Units

CS5012A CLKIN Frequency:

Internally Generated:

Externally Supplied: -7

-12

f

CLK

1.75

100 kHz

100 kHz

-

-

-

-

6.4

4.0

MHz

MHz

MHz

CS5014/5016 CLKIN Frequency:

Internally Generated: -14, -16

-28, -32

Externally Supplied: -14, -16

-28, -32

f

CLK

1.75

1

100 kHz

100 kHz

-

-

-

-

-

-

4

2

MHz

MHz

MHz

MHz

CLKIN Duty Cycle 40 - 60 %

Rise Times: Any Digital Input

Any Digital Output

t

rise

-

-

-

20

1.0

-

µs

ns

Fall Times: Any Digital Input

Any Digital Output

t

fall

-

-

-

20

1.0

-

µs

ns

HOLD Pulse Width t

hpw

1/f

CLK

+50 - t

c

ns

Conversion Time: CS5012A

CS5014

CS5016

t

c

49/f

CLK

+50

57/f

CLK

65/f

CLK

-

-

-

53/f

CLK

+235

61/f

CLK

+235

69/f

CLK

+235

ns

ns

ns

Data Delay Time t

dd

- 40 100 ns

EOC Pulse Width (Note 11) t

epw

4/f

CLK

-20 - - ns

Set Up Times: CAL,

INTRLV to CS Low

A0 to

CS and RD Low

t

cs

t

as

20

20

10

10

-

-

ns

ns

Hold Times:

CS or RD High to A0 Invalid

CS High to CAL, INTRLV Invalid

t

ah

t

ch

50

50

30

30

-

-

ns

ns

Access Times:

CS Low to Data Valid A, B, J, K

S, T

RD Low to Data Valid A, B, J, K

S, T

t

ca

t

ra

-

-

-

-

90

115

90

90

120

150

120

150

ns

ns

ns

ns

Output Float Delay: K, B

CS or RD High to Output Hi-Z T

t

fd

-

-

90

90

110

140

ns

ns

Serial Clock Pulse Width Low

Pulse Width High

t

pwl

t

pwh

-

-

2/f

CLK

2/f

CLK

-

-

ns

ns

Set Up Times: SDATA to SCLK Rising t

ss

2/f

CLK

-50 2/f

CLK

-ns

Hold Times: SCLK Rising to SDATA t

sh

2/f

CLK

-100 2/f

CLK

-ns

Notes: 11.

EOC remains low 4 CLKIN cycles if CS and RD are held low. Otherwise, it returns high

within 4 CLKIN cycles from the start of a data read operation or a conversion cycle.

CS5012A, CS5014, CS5016

2-14 DS14F6