LC876694B/78B/62B

No.6843-16/23

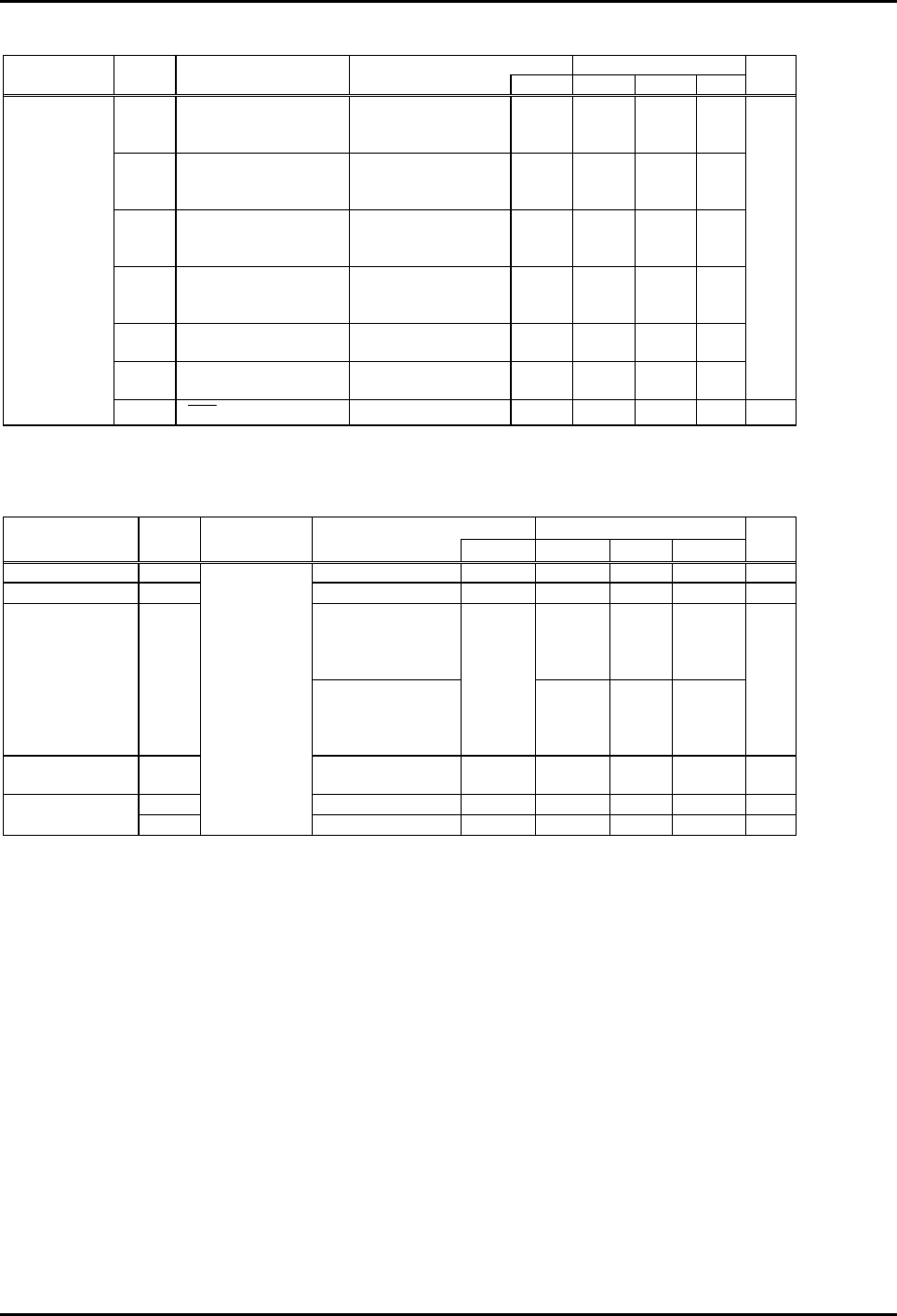

5. Pulse Input Conditions at Ta=-30

°

C to +70

°

C, VSS1=VSS2=0V

Ratings

Parameter Symbol Pins Conditions

VDD[V] min. typ. max.

unit

tPIH(1)

tPIL(1)

INT0(P70),

INT1(P71),

INT2(P72)

•Interrupt acceptable

•Events to timer 0 can

be input.

4.5 to 6.0 1

tPIH(2)

tPIL(2)

INT3(P73)

(Noise rejection ratio set

to 1/1.)

•Interrupt acceptable

•Events to timer 0 can

be input.

4.5 to 6.0 2

tPIH(3)

tPIL(3)

INT3(P73)

(Noise rejection ratio set

to 1/32.)

•Interrupt acceptable

•Events to timer 0 can

be input.

4.5 to 6.0 64

tPIH(4)

tPIL(4)

INT3(P73)

(Noise rejection ratio set

to 1/128.)

•Interrupt acceptable

•Events to timer 0 can

be input.

4.5 to 6.0 256

tPIH(5)

tPIL(5)

MICIN(P87) •Weak signal detection

counter enabled

4.5 to 6.0 1

tPIH(6)

tPIL(6)

NKIN(P72) •High speed clock

counter countable

4.5 to 6.0 1/12

t

CYC

High/low level

pulse width

tPIL(7)

RES

•Reset possible 4.5 to 6.0 200

µ

s

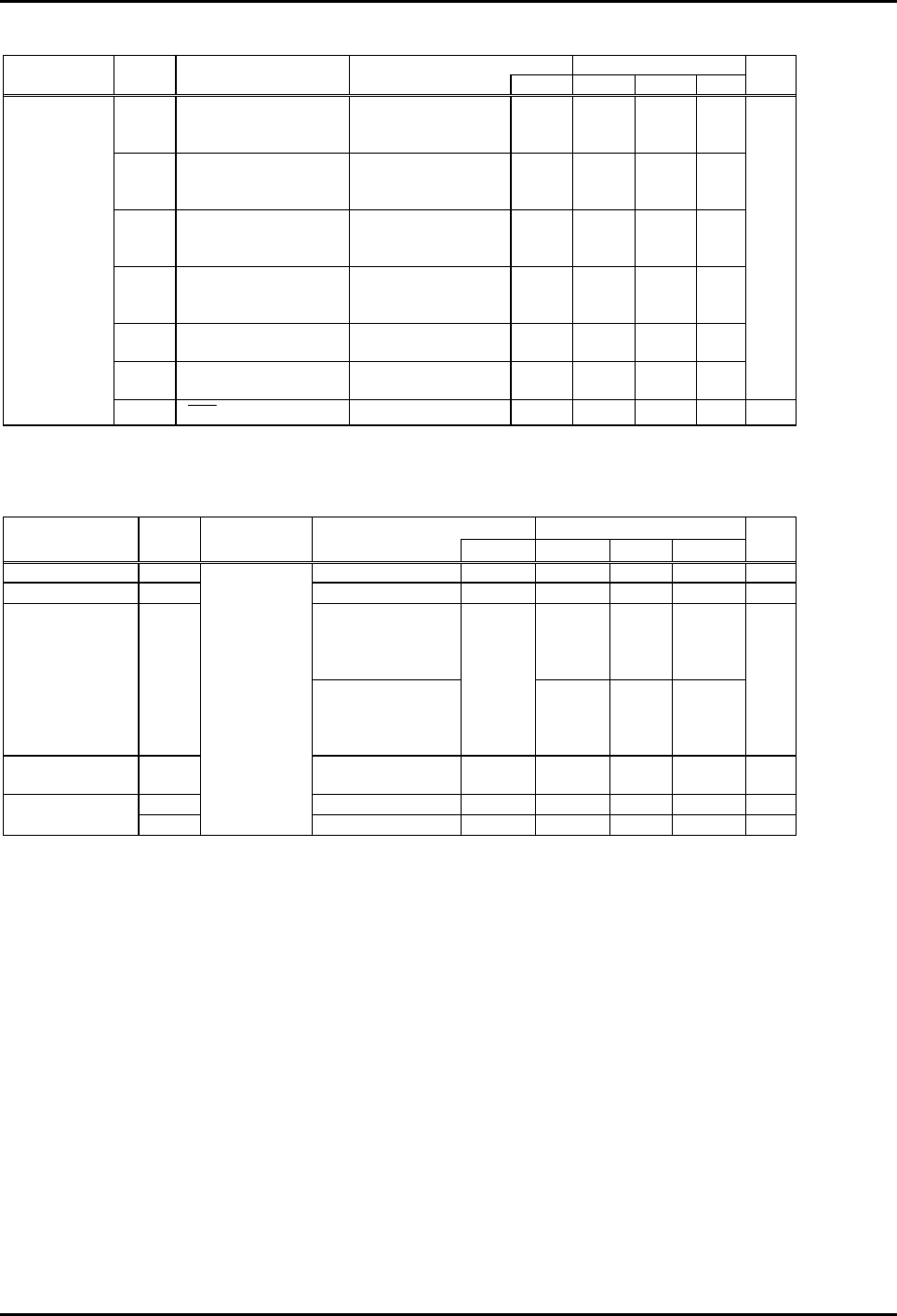

6. AD Converter Characteristics at Ta=-30

°

C to + 70

°

C, VSS1=VSS2=0V

Ratings

Parameter Symbol Pins Conditions

VDD[V] min. typ. max.

unit

Resolution N 4.5 to 6.0 8 bit

Absolute precision ET (Note2) 4.5 to 6.0

±

1.5

LSB

AD conversion time

= 32

×

tCYC

(ADCR2=0)

(Note 3)

15.62

(tCYC=

0.488

µ

s)

97.92

(tCYC=

3.06

µ

s)

Conversion time TCAD

AD conversion time

= 64

×

tCYC

(ADCR2=1)

(Note 3)

4.5 to 6.0

18.82

(tCYC=

0.294

µ

s)

97.92

(tCYC=

1.53

µ

s)

µ

s

Analog input

voltage range

VAIN 4.5 to 6.0 VSS VDD V

IAINH VAIN=VDD 4.5 to 6.0 1

µ

A

Analog port input

current

IAINL

AN0(P80) to

AN7(P87)

AN8(P70),

AN9(P71)

AN10(XT1),

AN11(XT2)

VAIN=VSS 4.5 to 6.0 -1

(Note 2) Absolute precision not including quantizing error (±1/2 LSB).

(Note 3) Conversion time means time from executing AD conversion instruction to loading complete digital value to register.