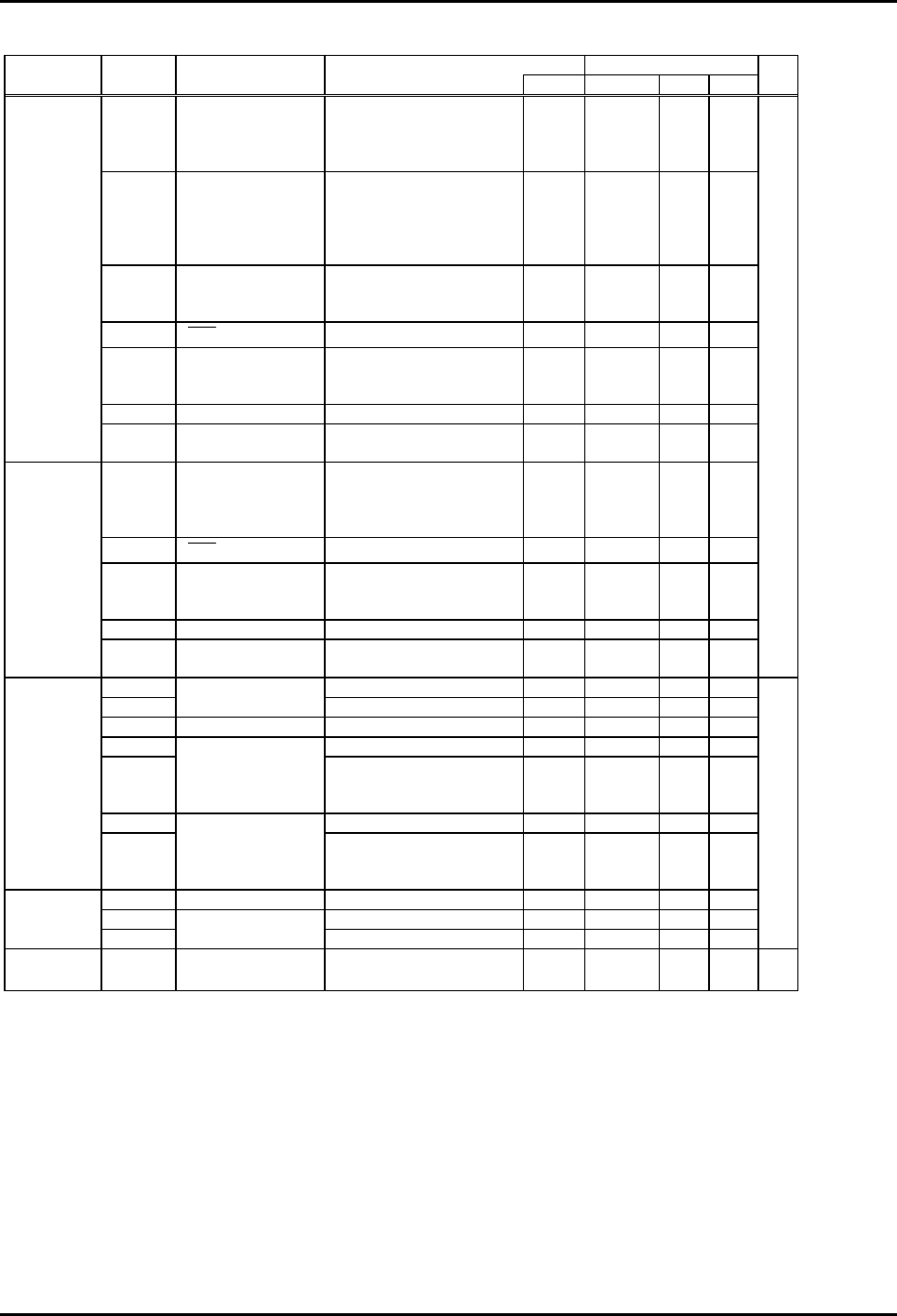

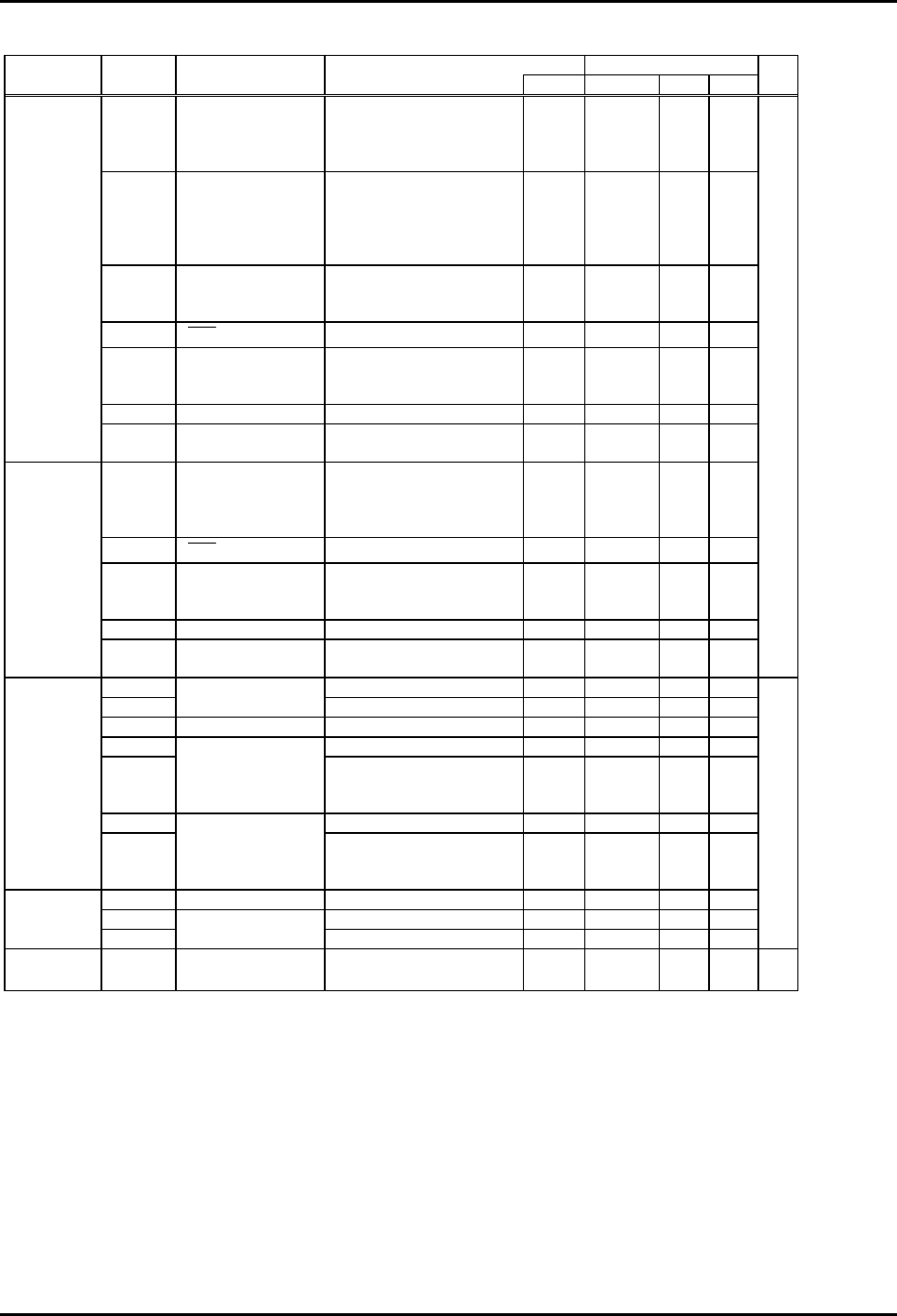

LC876694B/78B/62B

No.6843-13/23

3. Electrical Characteristics at Ta=-30

°

C to +70

°

C, VSS1=VSS2=0V

Ratings

Parameter Symbol Pins Conditions

VDD[V] min. typ. max.

unit

IIH(1) Ports 0,3: N-ch open

drain output

•Output disabled

•VIN=13.5V

(including OFF state leak

current of the output Tr.)

4.5 to 6.0 5

IIH(2) Port 0,1,3,7,8

•Output disabled

•Pull-up resister OFF.

•VIN=VDD

(including OFF state leak

current of the output Tr.)

4.5 to 6.0 1

IIH(3) S16 to S51 without

pull-down resister

(Port C,D,E,F,G)

When configured as an input

port

VIN=VDD

4.5 to 6.0 60

IIH(4)

RES

VIN=VDD 4.5 to 6.0 1

IIH(5) XT1,XT2 When configured as an input

port

VIN=VDD

4.5 to 6.0 1

IIH(6) CF1 VIN=VDD 4.5 to 6.0 15

Input high

current

IIH(7) P87/AN7/MICIN

weak signal input

VIN=VBIS+0.5V

(VBIS : Bias voltage)

4.5 to 6.0 4.2 8.5 15

IIL(1) Port 0,1,3,7,8 •Output disabled

•VIN=VSS

(including OFF state leak

current of the output Tr.)

4.5 to 6.0 -1

IIL(2)

RES

VIN=VSS 4.5 to 6.0 -1

IIL(3) XT1,XT2 When configured as an input

port

VIN=VSS

4.5 to 6.0 -1

IIL(4) CF1 VIN=VSS 4.5 to 6.0 -15

Input low

current

IIL(5) P87/AN7/MICIN

weak signal input

VIN=VBIS-0.5V

(VBIS : Bias voltage)

4.5 to 6.0 -15 -8.5 -4.2

µ

A

VOH(1) IOH=-1.0mA 4.5 to 6.0 VDD-1

VOH(2)

Port 0,1,3: CMOS

output option

IOH=-0.1mA 4.5 to 6.0 VDD-0.5

VOH(3) Port 7 IOH=-0.4mA 4.5 to 6.0 VDD-1

VOH(4) IOH=-20.0mA 4.5 to 6.0 VDD-1.8

VOH(5)

S0/T0–S15/T15

IOH=-1.0mA

IOH at any single pin is not

over 1mA.

4.5 to 6.0 VDD-1

VOH(6) IOH=-5.0mA 4.5 to 6.0 VDD-1.8

Output high

voltage

VOH(7)

S2+ to S51

IOH=-1.0mA

IOH at any single pin is not

over 1mA.

4.5 to 6.0 VDD-1

VOL(1) Port 02, 03 IOL=30mA 4.5 to 6.0 1.5

VOL(2) IOL=10mA 4.5 to 6.0 1.5

Output low

voltage

VOL(3)

Port 0,1,3

IOL=1.6mA 4.5 to 6.0 0.4

V

Pull-up

resistor

Rpu Port 0,1,3,7 VOH=0.9VDD 4.5 to 6.0 15 40 70

k

Ω

Continued