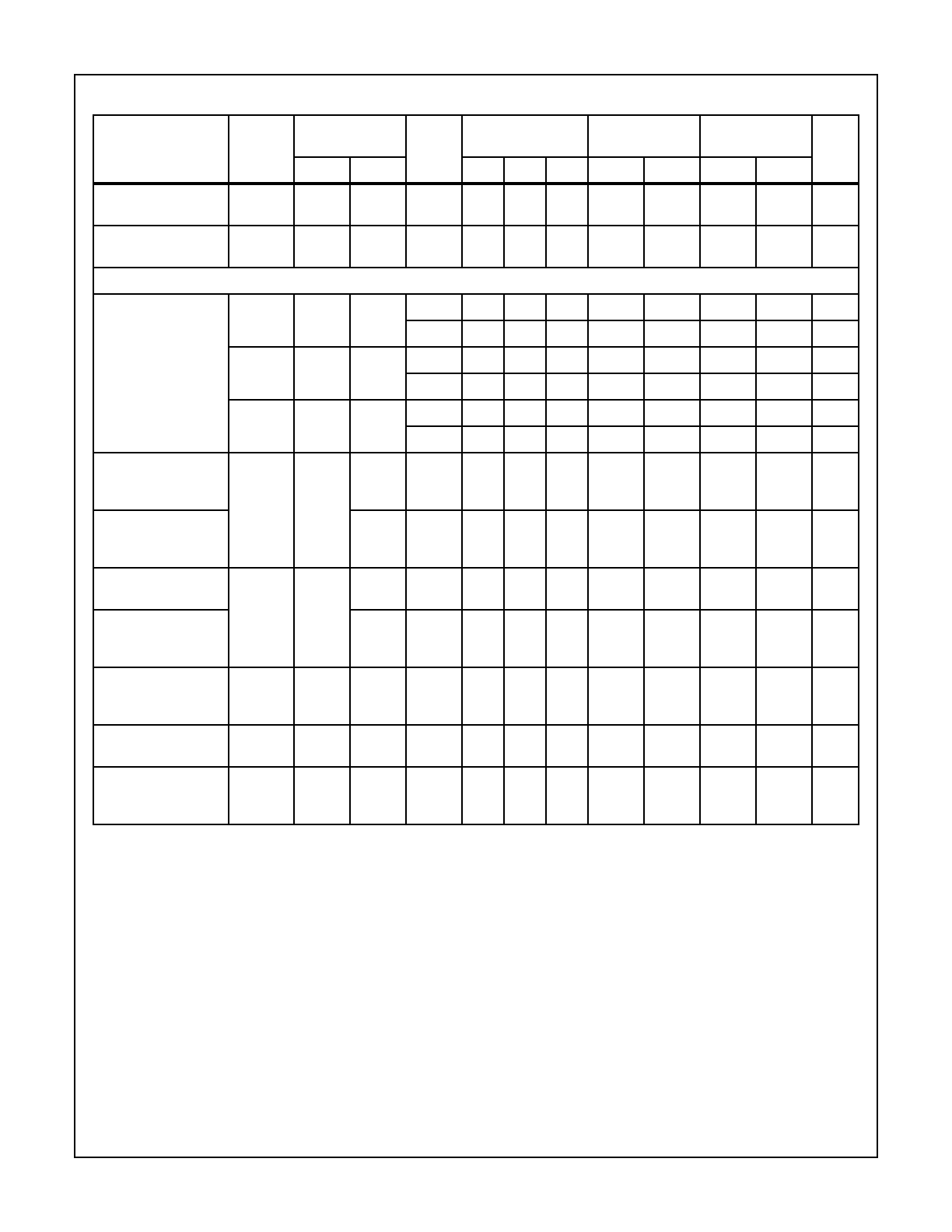

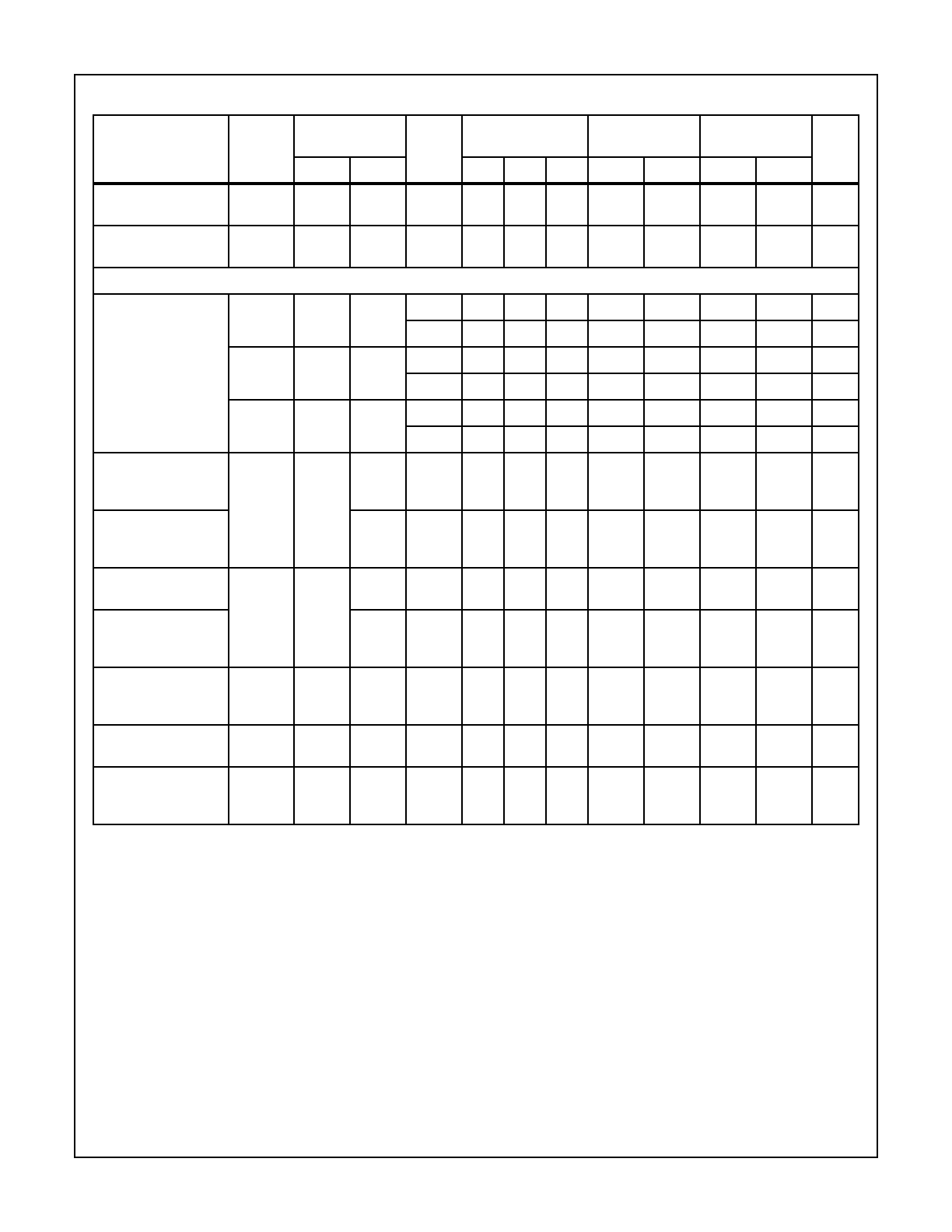

4

Input Leakage

Current

I

I

V

CC

or

GND

-6--±0.1 - ±1-±1 µA

Quiescent Device

Current

I

CC

V

CC

or

GND

0 6 - - 2 - 20 - 40 µA

HCT TYPES

Input Switch Points

(Note 2)

V

T

+ - - 4.5 1.2 - 1.9 1.2 1.9 1.2 1.9 V

5.5 1.4 - 2.1 1.4 2.1 1.4 2.1 V

V

T

- - - 4.5 0.5 - 1.2 0.5 1.2 0.5 1.2 V

5.5 0.6 - 1.4 0.6 1.4 0.6 1.4 V

V

H

- - 4.5 0.4 - 1.4 0.4 1.4 0.4 1.4 V

5.5 0.4 - 1.5 0.4 1.5 0.4 1.5 V

High Level Output

Voltage

CMOS Loads

-

V

T

+

or

V

T

-

-0.02 4.5 4.4 - - 4.4 - 4.4 - V

High Level Output

Voltage

TTL Loads

-4 4.5 3.98 - - 3.84 - 3.7 - V

Low Level Output

Voltage CMOS Loads

V

OL

V

T

+

or

V

T

-

0.02 4.5 - - 0.1 - 0.1 - 0.1 V

Low Level Output

Voltage

TTL Loads

4 4.5 - - 0.26 - 0.33 - 0.4 V

Input Leakage

Current

I

I

V

CC

and

GND

- 5.5 - - ±0.1 - ±1-±1 µA

Quiescent Device

Current

I

CC

V

CC

or

GND

0 5.5 - - 2 - 20 - 40 µA

Additional Quiescent

Device Current Per

Input Pin: 1 Unit Load

∆I

CC

(Note 3)

V

CC

- 2.1

- 4.5 to

5.5

- 100 360 - 450 - 490 µA

NOTES:

2. Hysteresis definition, characteristic and test setup see Test Circuits and Waveforms

3. For dual-supply systems theoretical worst case (V

I

= 2.4V, V

CC

= 5.5V) specification is 1.8mA.

DC Electrical Specifications (Continued)

PARAMETER SYMBOL

TEST

CONDITIONS

V

CC

(V)

25

o

C -40

o

C TO 85

o

C -55

o

C TO 125

o

C

UNITSV

I

(V) I

O

(mA) MIN TYP MAX MIN MAX MIN MAX

CD54HC132, CD74HC132, CD54HCT132, CD74HCT132